# **Flexible Circuit Design Guide** Fourth Edition

TELEDYNE ELECTRONIC TECHNOLOGIES

A Teledyne Technologies Company

# **Teledyne Electronic Technologies** Leading the interconnection field since 1963.

Teledyne Electronic Technologies (TET), formerly Teledyne Electro-Mechanisms, has been a leader in the field of interconnection technology since its incorporation in 1963. At that time we designed and manufactured innovative single layer flexible circuits and unique multilayer rigid-flex harnesses to support the NASA Saturn V program.

Throughout the years our design engineers and manufacturing personnel have worked together

perfecting solutions to customer design challenges from the simplest single layer applications to the most complex interconnection systems. TET is proud to hold numerous process patents related to flexible circuit manufacturing.

Today we continue to be in the forefront of the industry

by contributing to a multitude of military and commercial applications. In addition to the standard circuits we have produced for many years, TET is continuing to develop new and better products in the flexible circuit and multilayer rigid-flex marketplace.

Teledyne is committed to assisting our customers from design development right through prototypes and production. This commitment includes a fully

> staffed engineering department utilizing the latest CAD/CAM/CIM systems for circuit design, document creation, artwork generation, and drill/rout program creation. Our product engineers specialize in optimizing available tooling systems to help control costs.

110 Lowell Road, CS 68

Hudson, New Hampshire 03051

Tel: (603) 889-6191

Fax: (603) 882-4457

Email: sales@tetpct.com

# **Table of Contents**

| Table of Contents                                           | 3 |

|-------------------------------------------------------------|---|

| Design Guide Purpose and Use                                | 6 |

| Purpose of this Design Guide – Designing for Manufacture    | 7 |

| What the designer needs to know                             | 7 |

| Elevible Circuite                                           | 0 |

| Flexible Circuits                                           |   |

| What Is a Flexible Circuit?                                 |   |

| The Benefits of Flexible Circuits and How To Evaluate Them1 |   |

| Major Types of Flexible Circuits                            |   |

| Single-Sided Flexible Circuits                              |   |

| Access Methods                                              |   |

| Single Access Covered                                       |   |

| Double Access Covered                                       |   |

| Double-Sided Flexible Circuits                              | 5 |

| Multi-layer Flexible Circuitry                              | 6 |

| Rigid-Flex Circuitry1                                       | 7 |

| REGAL® Flex                                                 | 9 |

| REGAL® Flex 1                                               | 9 |

| REGAL® Flex 51                                              | 9 |

| Multi-Chip Modules (MCM)2                                   | 2 |

| Materials                                                   | Л |

| Conductive Materials                                        |   |

| Surface Treatments                                          |   |

| Foil Grades                                                 |   |

| Other Metals Used in Printed Wiring Boards                  |   |

| Flexible Dielectric Materials                               |   |

| Uses of Dielectric Films                                    |   |

| Adhesives                                                   |   |

| Thermoset Flexible Adhesives                                |   |

| Modified Acrylic Adhesive                                   |   |

| Epoxy Adhesives                                             |   |

| Reinforced Adhesive Materials                               |   |

| Pre-Impregnated Epoxy Glass                                 |   |

| Pre-Impregnated Polyimide Glass                             |   |

| Adhesiveless Materials                                      | 0 |

| Soldermask                                                  | 0 |

| Flexible Soldermasks                                        | 2 |

|                                                             |   |

| Electrical Design                       |

|-----------------------------------------|

| Conductor Thickness and Width           |

| Conductor Spacing                       |

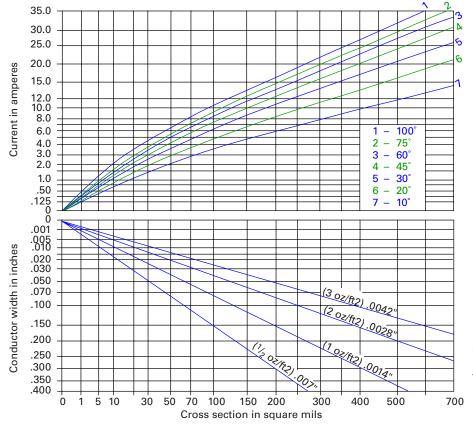

| Temperature Rise vs. Current            |

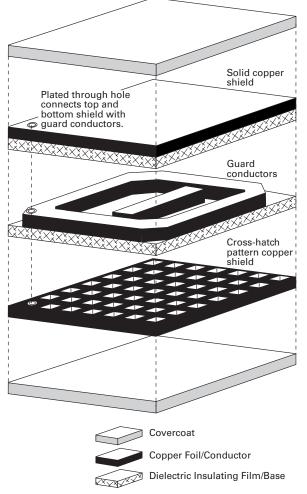

| Shielding                               |

| Dielectric Properties                   |

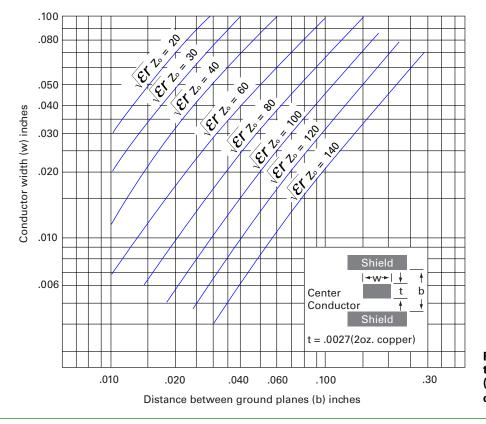

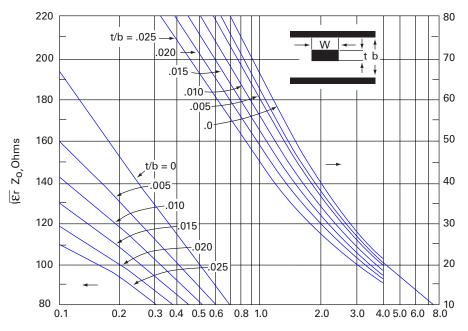

| Characteristic Impedance                |

| Calculations                            |

| High Frequency Lines                    |

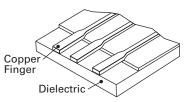

| Micro-Strip                             |

| Notes                                   |

| Distributed Capacitance                 |

|                                         |

| Mechanical Design43                     |

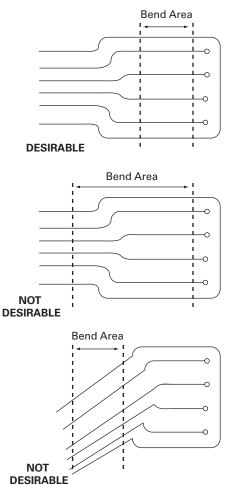

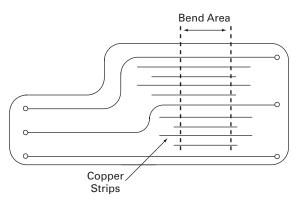

| Folding and Bending45                   |

| Continuous Flexing                      |

| Bend Radii                              |

| Flex Section Length                     |

| To Calculate Flex Length For 90° Bend46 |

| To Calculate Flex Length For 180° Bend  |

| Fold Areas                              |

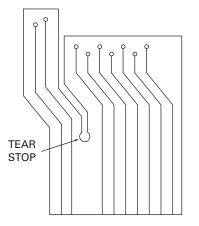

| Tear Stops                              |

| Terminal Baring                         |

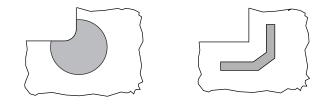

| Circuit Periphery                       |

| Shock and Vibration Considerations      |

| Rigid Reinforcement                     |

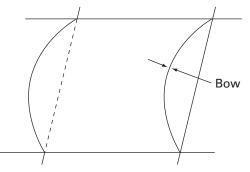

| Tolerances                              |

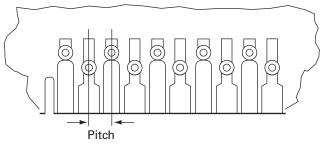

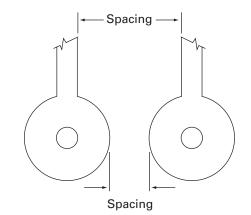

| Plated-Through Holes                    |

| Non-Plated-Through Holes                |

| Surface Mount Components                |

| Multi-Chip Modules (MCM)                |

| General Design                          |

| Materials                               |

| Thermal Considerations53                |

| Simplified Thermal Analysis54           |

| Board Layout                            |

| Component or Die Placement              |

| Wire Bonding to MCM-L Substrates        |

| Artwork Design                          |

| Automated Artwork                       |

| Supplied Artwork                        |

|                                         |

| General Artwork Design Rules            |

| Conductor Widths                        |

| Conductor Spacing                       |

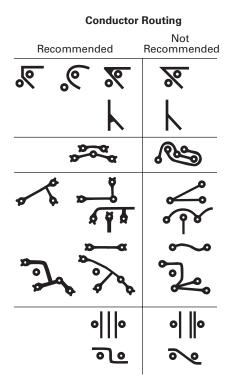

| Conductor Routing                       |

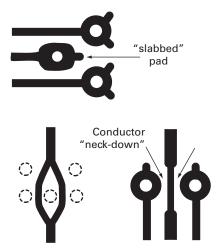

| Terminal Construction                                 |

|-------------------------------------------------------|

| Annular Ring                                          |

| Termination Pad Design for Non-Plated-Through Holes63 |

| Nomenclature Artwork and Component Designation        |

| Design Checklists64                                   |

| Electrical Design Checklist                           |

| Mechanical Design Checklist65                         |

| Fold Areas                                            |

| Circuit Profile                                       |

| Stiffeners and Reinforcements65                       |

| Tolerances                                            |

| Environmental                                         |

| Artwork Design Checklist66                            |

| Conductors                                            |

| Shielding                                             |

| Terminal Pads                                         |

| Glossary                                              |

| Industry Specifications                               |

# **Design Guide Purpose and Use**

# Purpose of this Design Guide – Designing for Manufacture

This Design Guide is provided to assist you in designing the most cost-effective flexible circuits for your electronic packaging needs. It is our belief that designers who are aware of the processes used in the manufacture of flexible printed circuits will be rewarded by a circuit design that will effectively make use of all the advantages that these types of electronic interconnects have to offer.

This Design Guide is meant to be a reference for the electrical, mechanical, and artwork considerations which must be addressed when designing a flexible circuit. As needed, the materials and processes used in their manufacture are described in detail so that informed tradeoffs and design decisions can be made. By following the guidelines presented here, your design will be both cost-effective and producible. When used as a design reference, this Design Guide is not meant to override any existing military specifications or commercial preferred design practices, but supports them both. The information contained herein is based on Teledyne Electronic Technologies' extensive experience as a designer and manufacturer of quality flexible and rigid-flex circuitry.

As you prepare to embark on a flexible circuit design program, Teledyne Electronic Technologies' design and engineering staff is on call to assist you. Please contact us with any questions regarding your electronic packaging needs.

## What the designer needs to know

There are many parameters that must be determined before beginning an electromechanical design incorporating flexible or multi-layer flexible circuitry. The designer must fully understand the electrical properties of the system, such as current maximums, voltages, types of signals (video, digital, RF, etc.), shielding considerations, impedance characteristics, and capacitance limitations. It is essential to define the circuit components selected, including connectors. To assist the manufacturer, the location of all components should be included. Also necessary is a detailed wire listing, net list and schematic. To allow the manufacturer the greatest amount of flexibility, only terminal areas, rather than specific pin-to-pin conductor runs, should be specified. This provides the manufacturer the necessary freedom to keep the circuit crossover points to a minimum, and reduce the total number of circuit layers necessary.

Please refer to the section of this guide titled *Electrical Design* for assistance in meeting the electrical concerns of your design. If you choose to have Teledyne's experienced staff of electromechanical designers provide a finished design, it will be necessary to provide the electrical parameters listed above to assure an electrically sound design.

After the electrical parameters are defined, the overall physical requirements of the system must be determined. As a minimum, the designer should be provided with dimensioned prints of the unit and appropriate cross-sectional views. Dimensioned prints should be clear and detailed to avoid costly tooling errors. On all prototype designs for fit evaluation only, Teledyne's product engineers will minimize tooling costs by taking the necessary steps.

The design of a flexible circuit interconnection system is facilitated by using an actual unit or an accurate mockup, or by using three dimensional software programs such as AutoCad or Pro- $E^{TM}$ , rather than relying solely on dimensioned prints. By using a box, a series of Mylar or paper "dolls" can be made to determine mechanical

Figure 1-1. "Mylar doll" cutout

## **Design Guide Purpose and Use**

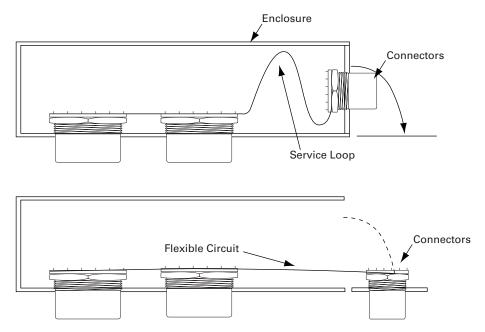

approaches and general configurations. The unit or mock-up should have all the required hardware installed to make the design complete and prevent physical interference. Refer to Figure 1-1. The flex harness must be designed to fit the general assembly sequence of its unit, so the cables do not cover any components that may require service or replacement. Cables should not be routed over an area where a component must be installed after the assembly is completed. If the flexible section of the unit will be designed to flex when the box is opened, then an adequate "service loop" should be incorporated in the design. This service loop should be

long enough to allow access to the inside of the unit but should not interfere with any other components when installed. Refer to Figure 1-2.

The final consideration is the environmental conditions to which the system will be subjected. Thermal rises, atmospheric conditions, humidity, vibration, and handling are all environmental factors that can influence design criteria. Adequate strain relief and sealing must be provided for moisture and vibration applications. If the unit is subjected to constant thermal cycling, special consideration must be used when choosing insulating and bonding materials.

Figure 1-2. A service loop should be used when opening the package results in circuit flexing.

# **Chapter Terms**

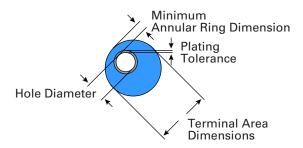

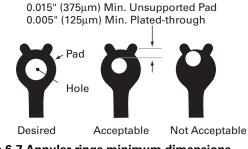

**Annular Ring:** That portion of a conductive material completely surrounding a hole.

**Barrel Cracks:** Cracks that appear in the electro-plating inside a plated through hole due to mechanical and thermal stresses.

**Basestock:** The insulating material upon which a conductive pattern may be formed.

Base Material: See Basestock.

**Blister:** Delamination in the form a localized swelling and separation between any of the layers of a laminate base material, or between base material and conductive foil or protective coating.

**Coefficient of Thermal Expansion (CTE):** The linear dimensional change of a material per unit change in temperature.

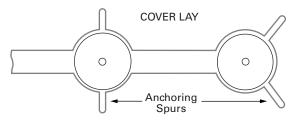

**Covercoat, Cover Lay or Cover Layer:** The layer of insulating material that is applied over a conductive pattern on the outer surface of a printed circuit. Used for electrical insulation and environmental sealing.

**Delamination:** A separation between plies within a base material, between a base material and a conductive foil, or any other planar separation within a multi-layer printed board. See also Blister.

**Dielectric:** A material with a high resistance to the flow of electrical current.

**DIP/Dual-in-Line Package:** An IC package having pins that protrude through the substrate on which it is mounted. Electrical connection is usually made by soldering to the reverse side of the substrate to which the device is mounted.

**Double-Sided Printed Board:** A printed board with a conductive pattern on both of its sides.

**Electro-deposited (Copper):** The deposition of a conductive material (copper) from a plating solution by the application of electrical current.

**Epoxy Prepreg:** A glass impregnated epoxy adhesive material used to bond multiple layers, with high mechanical stability in all axes.

**Etching:** The chemical, or chemical and electrolytic, removal of unwanted portions of conductive or resistive material.

**Flexible Printed Circuit:** A patterned arrangement of printed circuitry and components that utilizes a flexible base material with, or without a flexible cover lay. See Flexible Printed Wiring.

**Flexible Printed Wiring:** A patterned arrangement of printed wiring and components that utilizes a flexible base material with, or without a flexible cover lay. See Flexible Printed Circuit.

**Glass Transition Temperature (Tg):** The temperature at which an amorphous polymer, or the amorphous regions in a partially-crystalline polymer, changes from being in a hard and relatively brittle condition, to being in a viscous or rubbery condition.

**Hold-Down Tabs:** Conductive tabs extending from the outside of an annular ring or other termination pad used to help secure the pad to the substrate.

**Interfacial Area:** The boundary between the flexible and rigid sections of a rigid-flex circuit assembly.

**Modified Acrylic Adhesive:** An adhesive material commonly used in multi-layer flexible circuits.

**Multilayer Printed Board:** The general term for a printed board that consists of rigid or flexible insulation materials and three or more alternate printed wiring and/ or printed circuit layers that have been bonded together and electrically interconnected.

**Multilayer Printed Circuit Board Assembly:** An assembly that uses a multi-layer printed circuit board for component mounting and interconnecting purposes.

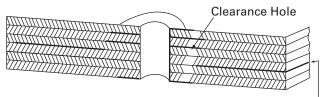

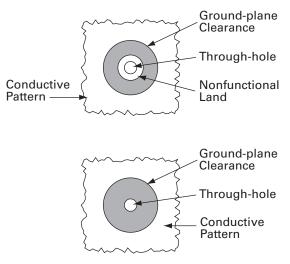

**Plated-Through Holes:** A hole with plating on its walls that makes an electrical connection between conductive patterns on internal layers, external layers, or both, of a printed board.

**Polyimide:** A dielectric film material commonly used for flexible circuit fabrication as an insulating layer.

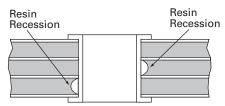

**Resin Recession:** The presence of voids between the parallel of a plated-through hole and the wall of the hole as seen in microsections of plated-through holes that have been exposed to high temperatures.

**Rigid-Flex Printed Board:** A printed board with both rigid and flexible base materials.

**Single-Sided Printed Board:** A printed board with a conductive pattern on one of its sides.

**SMD/Surface Mount Device:** Any active or passive component packaged such that electrical and mechanical contact is achieved on the top surface only of the substrate on which it is mounted.

**Terminal Pad:** A portion of a conductive pattern that is usually used for making electrical connections, for component attachment, or both.

**Through-Hole Technology:** Techniques used to connect electrical components to a conductive pattern by the use of component holes.

**Vertical Pins:** A type of termination which connects two conductor runs in a solder assembly where the runs are in two different layers.

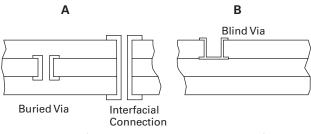

**Vias:** A plated-through hole that is used as an interlayer connection, but in which there is no intention to insert a component lead or other reinforcing material.

# What Is a Flexible Circuit?

In its simplest form, a flexible circuit is a pattern of conductors printed on a flexible dielectric (insulating) film. The technology to print electronic circuits on flexible materials was developed in the 1950's in response to the Space Program's need to save weight and space. The relatively simple single-sided and double-sided circuits from that time have evolved into multi-layer circuits and combination rigid-flexible circuit assemblies which provide total electronic packaging solutions. Applications for flexible circuits today span the full scope of the electronics marketplace - from military and aerospace, to telecommunications and computers; from industrial controls and process equipment, to automotive instrumentation; from consumer goods to toys. The expanding application for this technology fuels its evolution as a cornerstone in the quest for better electronic packaging.

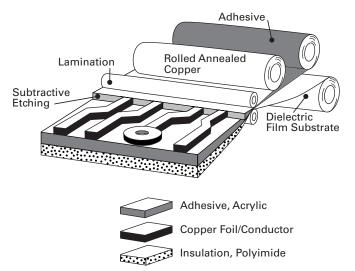

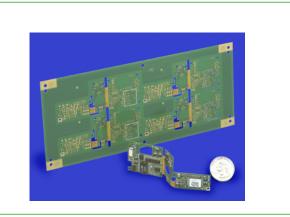

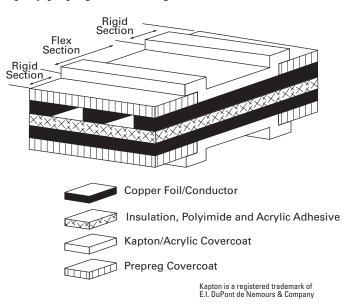

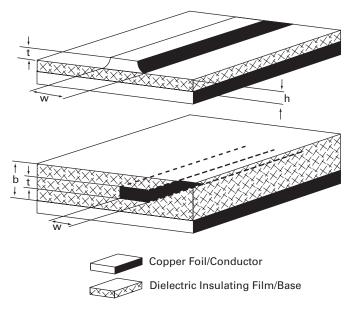

Figure 2-1. Basic flexible circuit construction.

Flexible circuitry can be designed to achieve maximum savings in assembly time, weight, space and cost. Flexi-

ble circuitry and rigid-flex circuits have a higher degree of reliability because of the decreased need for interconnection hardware normally used in conventional electronic packaging. Flexible circuit packaging reduces the chance of human error in installation and permits highly repeatable production assembly.

# The Benefits of Flexible Circuits and How To Evaluate Them

In addition to the savings in assembly time, weight, space and cost, the flex conductor's flat form provides about 50% more surface area than a round wire of equivalent cross-section. This provides greater heat dissipation and a higher current carrying capacity. Smaller conductor widths using lighter weight materials and very thin insulating materials can be used to carry the same current to further aid in weight and volume reductions. The overall reduction in weight and volume expected can be up to 70% as compared to a similar design using conventional round wiring harness methods.

Despite the advantages, not every packaging problem can be economically solved by the use of flexible circuitry. There are several factors that must be examined to be sure that this type of packaging would be the most cost-effective and still meet all mechanical, electrical, and thermal parameters. If cost is a major concern, then the total installed cost of the competing interconnect system must be considered against using flexible circuitry in the electronic interconnect system. A correctly designed flexible or multi-layer flexible circuit can reduce not only weight and volume, but also the amount of connectors and other independent connection devices. The combined costs of the procurement, storage and assembly of all these independent pieces must factor into any cost evaluation.

Figure 2-2. Comparison of "before" and "after" designs.

Figure 2-3. Quality engineered appearance example.

Overall circuit complexity and the total number of circuits that will be required must also be considered. If a circuit design is relatively simple, if total volume is low, and if space is available, conventional interconnect methods would likely be the most cost-effective. However, if the circuit is more complex, consisting of many signals or requiring specific electrical or mechanical requirements, then flexible circuitry would be the better design choice.

# **Major Types of Flexible Circuits**

Flexible circuits can be designed and manufactured to meet a wide variety of interconnect requirements. From the simplest single-sided circuit, to multi-layer circuits with 40 layers or more, each is constructed using the same materials and techniques. Their materials and construction are described below.

## **Single-Sided Flexible Circuits**

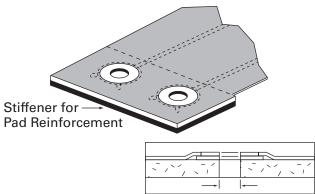

# Single-sided flexible material with or without shield(s) or stiffener(s) (one conductor layer)

The single layer flexible circuit is the simplest and easiest to manufacture and is used primarily for point-topoint wiring. A wide choice of conductor thickness, widths and shapes, as well as connector attachments and termination pads are available. It is usually constructed of a single layer of copper foil laminated to a flexible substrate insulating dielectric film. Another layer of flexible dielectric film, known as the covercoat, is laminated to the imaged and etched copper substrate, encapsulating the conductors to provide electrical insulation and protection from the environment. The design of a layer of circuitry for a single layer can be as simple as a solid copper plane with only one solderable connection, to a multitude of conductors and terminal pads spread over a sheet as large as 24 X 30 inches (610 X 762 mm). Multiple single layers can be used together to make a complex assembly that consists of interconnects using either pins, connectors or other electrical components. Single-sided circuits can be supplied in different ways to meet specific application needs. Refer to Figure 2-4.

Figure 2-4. Single-sided circuit construction.

There are three basic types of single-sided flexible circuits, presented in order of increasing cost – single access uncovered, single access covered, and double access covered. Each is described as follows.

# **THE BASICS**

## **BASIC FLEX CIRCUIT MATERIALS**

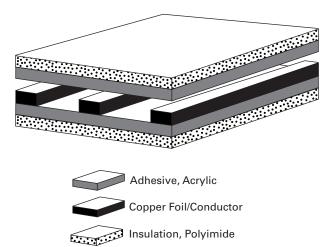

There are a number of materials used in the manufacture of flexible circuits. Please refer to the *Materials* Section for detailed information regarding these materials. This is basic information on the material types used to aid in an understanding of this section on the types and construction of flexible circuits.

There are three fundamental types of materials used in fabricating flexible circuits — conductor, dielectric or insulator film, and adhesive. Each is described below.

**Conductors** — Copper foil is the conductor material of choice with the electrical and physical properties necessary to withstand both the manufacturing processes and the environments in which flexible circuits are typically used. The copper foil is bonded to a base dielectric or insulator film

material using an adhesive film. The copper foil is typically coated with a photo-sensitive layer which results in the desired pattern of conductors and termination pads after exposure and etching processes.

**Dielectric or Insulator Film** — Dielectric or insulating films are used to provide the base on which the copper foil conductor layer(s) are attached. The most common dielectric film material is polyimide.

**Adhesives** — Adhesive films provide the material to bond the copper foil to the base film. An adhesive film layer is sandwiched between the copper foil and dielectric base film, and the multi-layer "sandwich" is laminated using heat and pressure.

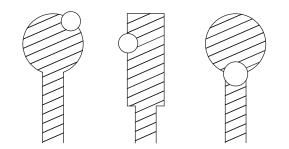

### **Access Methods**

Access to a pattern is accomplished in one of two ways, depending on whether access to one or both sides of a pattern is required. Each method is described as follows.

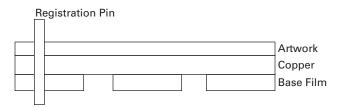

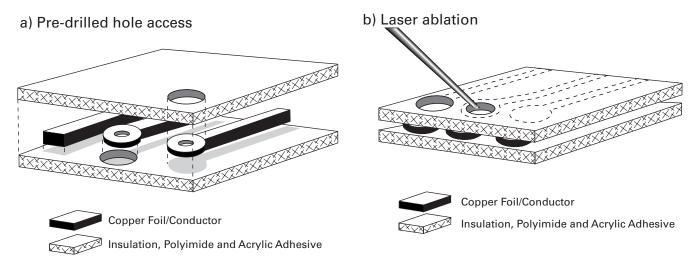

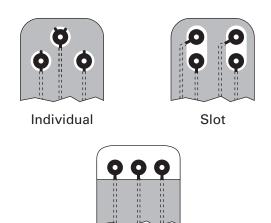

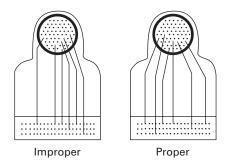

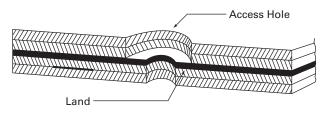

To gain access to one side of a pattern, holes are predrilled in the base dielectric film or covercoat prior to laminating the copper foil. The artwork pattern must be accurately positioned to match the location of the predrilled holes from the copper side. Since the operator cannot see the pre-drilled holes through the copper, this alignment must be accomplished using alignment pins. The circuit is then covercoated using a pre-drilled covercoat in the same manner as a single access covered circuit. Refer to Figure 2-5.

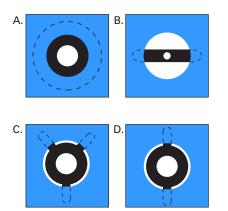

#### Figure 2-5. Access Methods

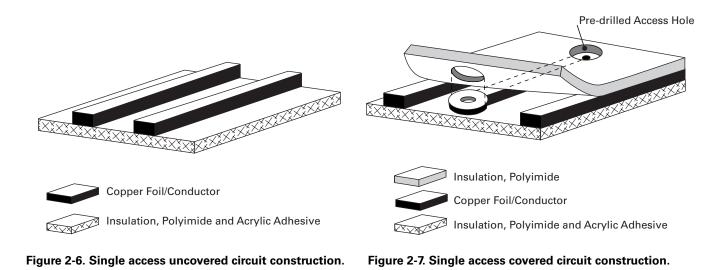

#### **Single Access Uncovered**

This type of single layer flexible circuit is the most inexpensive. It consists of a base dielectric film and copper foil that is imaged and etched. Because there is no protective covercoat laminated to the etched pattern, the expense of the covercoat and processing is eliminated. This type of circuitry is normally used in applications where the circuit will not be exposed to an adverse environment or to harsh mechanical abuse. Typical applications are telephones, toys and other consumer goods which are typically small, enclosed items. Refer to Figure 2-6.

#### **Single Access Covered**

Circuits made using this method are the same as the single access uncovered, except for a flexible dielectric film laminated to encapsulate the conductors for both electrical insulation and protection from the environment. The pre-drilled holes are aligned to the terminal pads prior to covercoat lamination to provide access to the pads. Refer to Figure 2-7.

#### **Double Access Covered**

This type of single layer circuit, known also as reverse bared, is the most expensive of the three single-sided assembly techniques. It allows access to a circuit from both sides, while also providing the environmental protection of insulating material on both sides of the copper conductors. Refer to Figure 2-8.

Access to both sides of a single layer flexible circuit is achieved by milling the covercoat material from the base material with a laser after the covercoat is applied. This process will yield near-perfect registration to the pad, but is tedious and time consuming. Both of these methods increase the circuit cost because of increased labor and decreased yields. Refer to Figure 2-5.

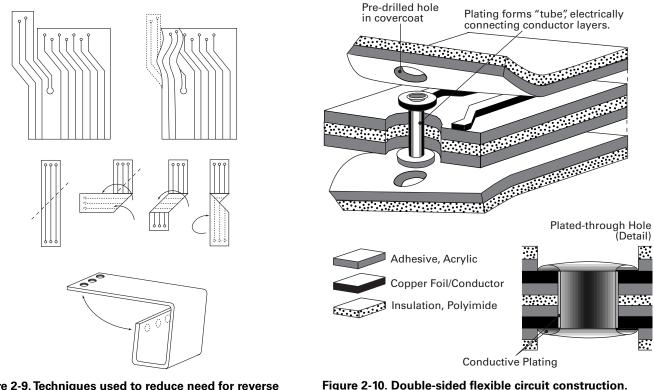

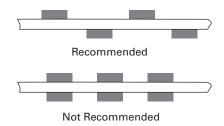

There are several folding techniques that can be employed to reduce or eliminate the need for reverse baring of the solder pads. Each reduces or eliminates the need for reverse baring of the solder pads by physically moving the bottom access to the top plane. These methods are shown in Figure 2-9 and should be considered prior to designing a circuit requiring reverse baring.

Figure 2-8. Double access covered circuit construction; a) pre-drilled hole access; b) laser ablation.

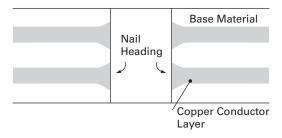

# **Double-Sided Flexible Circuits**

Double-sided flexible material, with or without shield(s) or stiffener(s) (two conductor layers); with plated-through holes

A double-sided flexible circuit allows for more complex point-to-point wiring using almost the same space as a single-sided flex circuit. Double-sided circuits consist of a flexible base dielectric material with copper foil laminated to both surfaces. This allows for a design that utilizes conductors on both sides of the dielectric substrate for more efficient packaging. The conductors can be connected electrically by using plated-through hole technology. A flexible insulating dielectric is used to encapsulate the etched pattern to provide electrical insulation and protection from the environment. This covercoat material must have the terminal location hole drilled prior to lamination to allow access to the terminal pads. Refer to Figure 2-10.

Figure 2-9. Techniques used to reduce need for reverse baring of solder pads.

When the circuit is designed to use plated-through holes, hold-down tabs on the terminal pads are not necessary, since the plating provides support to the pad area. This means that a higher density design can be achieved in the termination area without violating any conductor-to-pad spacing requirement. Unsupported or non-plated pads require hold-down tabs to provide the necessary mechanical support.

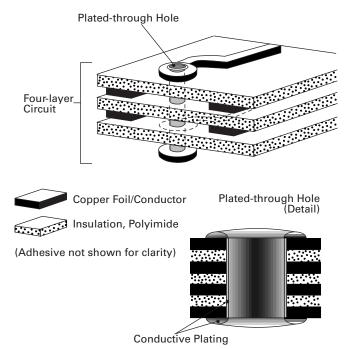

## **Multi-layer Flexible Circuitry**

Multi-layer flexible material, with or without shield(s) or stiffener(s) (more than two conductor layers); with plated-through holes

Multi-layer circuits allow very high density packaging using complex point-to-point wiring. They can integrate systems requiring multiple interconnections into one unit, thereby reducing assembly time, cutting weight and volume, and increasing reliability. Typical applications for these types of circuits are those that must have shielded conductors, where impedance control is necessary, or where several layers of circuitry must access different areas. Because all holes can be drilled and plated-through, a designer can access several internal pads or circuit layers on each connector pin without having to use multiple soldering operations. Refer to Figure 2-11.

Multi-layer flexible circuits can be designed to meet most of the electrical, mechanical and environmental conditions found in both military and commercial applications. These technologies provide a wide choice of

Figure 2-11. Multi-layer circuit construction.

conductor configurations and terminations. They can be designed with as few as four layers, or to 24 or more layers. Each of these types is discussed separately to show their particular benefits and constraints.

Multi-layer flexible circuits consist of multiple singleor double-sided flexible circuits laminated together to form an integral component. They can be bonded over their entire surface or bonded only in selective regions to allow increased flexibility, as shown in Figure 2-11. When fully bonded, multi-layer circuits become increasingly less flexible as the number of conductive layers increases. Full bonding is recommended only with four or fewer layers. When more layers are required, the bonding adhesive should be removed in sections designed to bend or form.

A variety of insulating materials is available for innerlayer substrate and covercoating of the flexible layer. The most commonly used is polyimide film, which is available in thicknesses ranging from 0.001" to 0.005" ( $25\mu$ m to  $125\mu$ m), with modified acrylic adhesive thicknesses ranging from 0.001" to 0.003" ( $25\mu$ m to  $75\mu$ m). Other thicknesses are available at extra cost, but should be considered only for special requirements.

The most common copper weights used in multi-layer flex circuits are 1 oz.  $(35\mu m)$  and 2 oz.  $(70\mu m)$ ; Teledyne has produced circuits using 6 oz.  $(210\mu m)$  copper. Since flexibility decreases as the copper weight increases, designs should specify the thinnest copper possible without compromising electrical requirements.

The various methods of processing multi-layer flexible circuits each have their advantages and disadvantages. In fully bonded circuits for example, double adhesivecoated insulating material, usually polyimide film, can be used to bond layers together, which eliminates the need for covercoating individual layers, cutting both material and labor cost. But, as previously noted, the number of layers that can be laminated together and still maintain flexibility is limited. To achieve flexibility with higher layer counts, selected areas are left unbonded. Those areas which are bonded, however, must do so where the layers are already covercoated using a modified acrylic adhesive. This is a significant source of mechanical failure because the bond strength between a processed polyimide film covercoat and acrylic adhesive is marginal and subject to delamination. In addition, the acrylic adhesive is thermally unstable in regards to low Tg, and high CTE. When used in a board requiring plated-through hole processing, this introduces a variety of problems ranging from barrel cracks to resin recession. These problems compound as circuit thickness

increases due to the added acrylic adhesive. To ensure thermal stability, materials are used which possess very high glass transition temperatures (Tg) and low coefficient of thermal expansion (CTE). Please refer to the discussion of *REGAL*® *Flex* later in this section for the best procedure for designing a thermally stable multilayer flexible circuit.

## **Rigid-Flex Circuitry**

Multi-layer, rigid and flexible material combinations (more than two conductor layers); with plated-through holes

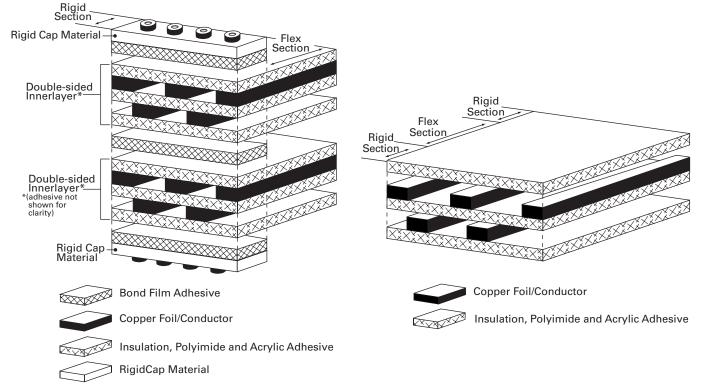

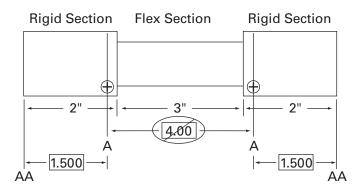

Rigid-Flex circuits, like multi-layer circuits, allow very high density packaging using complex point-to-point wiring, can integrate systems requiring multiple interconnections into one unit, and can provide significant reductions in assembly time, weight, and volume, while increasing reliability. Typical applications for rigid-flex circuits are the same as for multi-layer circuits. Unlike multi-layer circuitry, rigid-flex circuits can have both surface-mount and through-hole components mounted in rigidized areas without risking damage from flexing. Again, like multi-layer circuits, rigid-flex circuits can be designed to meet most of the electrical, mechanical and environmental conditions found in both military and commercial applications, providing a wide choice of conductor configurations and terminations, with as few as four layers, or to 24 or more layers. Refer to Figure 2-12.

A rigid-flex circuit consists of multiple flexible wiring layers, selectively bonded together using an adhesive. A cap layer of rigid core, copper clad laminate is bonded to the top and bottom of the circuit to further add stability to the bonded areas. It is in these bonded areas that the circuit board will be drilled and plated-through to provide the necessary Z-axis interconnects between the flexible wiring layers. Components are mounted on rigid sections. Figure 2-12 shows the traditional construction used for most applications.

As shown in Figure 2-13, the flexible printed wiring (inner) layers consist of a flexible base dielectric with rolled annealed copper bonded on one or both sides. Because of its grain structure, rolled annealed copper is more flexible than electro-deposited copper. After this substrate is imaged and etched using conventional processing equipment, a cover layer dielectric is applied to encapsulate the copper traces. This covercoat electrically insulates the conductors and shields them from the environment.

Rigid-flex assemblies can only be manufactured using this process and these materials in limited quantities. The flexible dielectric materials used in their manufacture have properties that make these materials unsuitable for multi-layer processing. First, the acrylic adhesive

Figure 2-12. Traditional rigid-flex circuit construction.

Figure 2-13. Traditional rigid-flex innerlayer construction.

| Material                   | Moisture<br>Absorption<br>(% by<br>Weight) | <b>CTE</b><br>Z Axis<br>(ppm/<br>°C) | <b>Т</b> д<br>(°С) |

|----------------------------|--------------------------------------------|--------------------------------------|--------------------|

| Acrylic<br>Adhesive        | 4                                          | 425                                  | 40                 |

| Epoxy<br>Prepreg           | 2.2                                        | 85                                   | 130                |

| Polyimide<br>Film          | 1.33                                       | 48                                   | 390                |

| Polyimide<br>Prepreg       | 0.7                                        | 55                                   | 210                |

| HighTg<br>Epoxy<br>Prepreg | 1.75                                       | 70                                   | 170                |

Material Characteristics

Table 2-1. Shows comparative data for several materialsfor both moisture absorption and CTE.

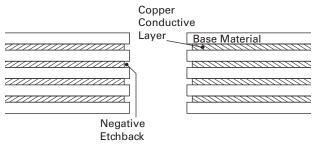

has a high moisture absorption characteristic of approximately 4% by weight. The polyimide film also absorbs moisture, but at a lower rate of approximately 3% by weight. Moisture absorption affects the multiple layers in two ways. The basestock itself is unstable in the X and Y axis because of the growth and shrinkage of the material due to the moisture content, leading to a layerto-layer registration problem during lamination on high density circuit boards. Moisture also affects the quality of the circuit board by outgassing during extreme thermal rises, such as soldering. Outgassing of moisture causes delamination, resin recession and "blow outs" in the plated-through holes. Moisture can be driven out of the material by proper pre-baking of the circuit prior to any temperature excursions.

Another property of the acrylic adhesive that makes it unsuitable for use in multi-layer boards is its high coefficient of thermal expansion (CTE) above its glass transition temperature (Tg) — the CTE of acrylic is approximately 425 ppm/°C as compared to 70 to 85 ppm/°C for most epoxy prepreg materials. This high CTE means that the material has a high Z-axis expansion rate. During thermal rises the acrylic adhesive expands at a higher rate than the other materials used in the construction. Defects such as barrel cracks, outer layer pad lift, and delamination can result from the thermal instability of the acrylic adhesive. To achieve increased reliability and higher layer counts, the amount of acrylic adhesive must be limited or eliminated in the rigidized areas. This can be accomplished by processing the innerlayer basestock on a polyimide/acrylic base and then using a selective covercoating method whereby the polyimide/acrylic adhesive material is laminated in the flex area only. The conductor traces in the board area are covercoated using an epoxy prepreg. Refer to Figure 2-14.

Figure 2-14. Hybrid rigid-flex inner layer.

To provide electrical insulation reliability, the manufacturer must engineer into the tooling scheme an overlap of these separate dielectrics to prevent shorting between subsequent layers and to ensure environmental sealing. By using prepreg bond films to bond all the layers together, the amount of acrylic adhesive is further reduced. This technique allows the use of polyimide/ acrylic materials to be minimized in the rigid areas of the circuit board. The major drawback to this construction is the X- and Y-axis instability of the base material, which leads to problems with layer-to-layer registration during final lamination.

| Туре | Common<br>Name                                                           | Layer Composition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Single-<br>sided                                                         | тор<br>••••••••••••••••••••••••••••••••••••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2    | Double-<br>sided,<br>plated<br>through<br>holes                          | **************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3    | Multi-<br>layer,<br>flexible<br>plated<br>through<br>holes               | TOP<br>3 layers<br>min. to<br>12 layers<br>max.<br>BOTTOM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4    | Rigid-<br>flex,<br>multi-<br>layer<br>with<br>plated<br>through<br>holes | Rigid Flexible Rigid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5    | Multi-<br>layer, no<br>plated<br>though<br>hole                          | Mathematical         Mathematical< |

## **Types of Flexible Circuits**

# Rigid Laminate Copper Foil/Conductor Insulation, Polyimide and Acrylic Adhesive Prepreg Bond Film Prepreg Covercoat

Table 2-2.

## **REGAL® Flex**

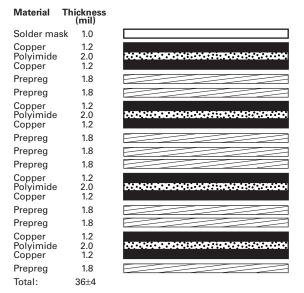

Teledyne Electronic Technologies has successfully developed a process that completely eliminates all polyimide films and acrylic adhesives in the hardboard areas of a rigid-flex circuit. This patented manufacturing process, known as REGAL® Flex, produces a rigid-flex assembly that is thermally stable and offers ultra-high density.

# **REGAL® Flex 1**

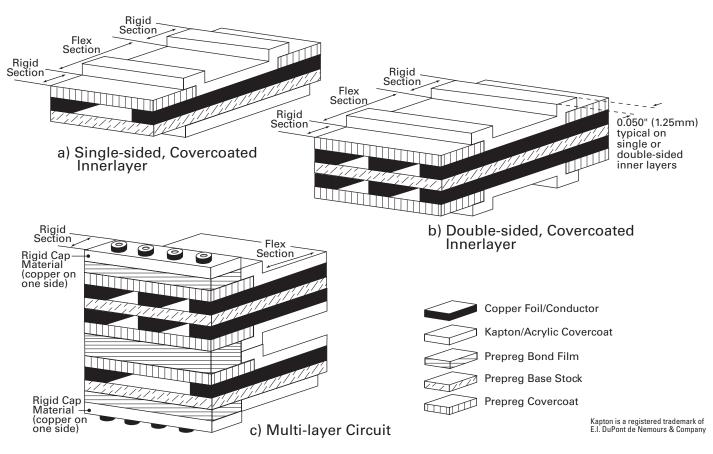

The REGAL<sup>®</sup> Flex process substitutes the polyimide/ acrylic base materials normally bonded to the selected copper, with an epoxy prepreg material to create a single or double-sided clad base laminate. Coverlays of polyimide/acrylic materials are then registered and laminated at flexible areas only, after image and etch operations are complete. These circuit layers can now be stacked for multi-layer circuit lamination using epoxy prepreg bond plies, registered in place at the rigidized sections of the circuit. Refer to Figure 2-15.

This process results in a more stable x, y and z-axis circuit for component assembly at the rigidized sections by eliminating the higher moisture content materials from these areas. The flex area is slightly less flexible due to the prepreg usage on the base stock. However, final flexibility exceeds flex-to-install requirements and provides for a lower cost lamination process.

The resulting covercoated layers are then selectively bonded using a pre-windowed epoxy prepreg bond film to allow for rigidizing selective areas for subsequent through-hole processing. The methods used to produce this type of rigid-flex board are the same as those used to manufacture an all polyimide film/acrylic construction board. The major difference is the materials used when processing.

Both of these manufacturing techniques can be used on applications that require the flexible section to bend during installation, normally not more than 90°. Circuit boards manufactured using these techniques have exceeded the military specification for a flex-to-install application of 25 or more flexing cycles.

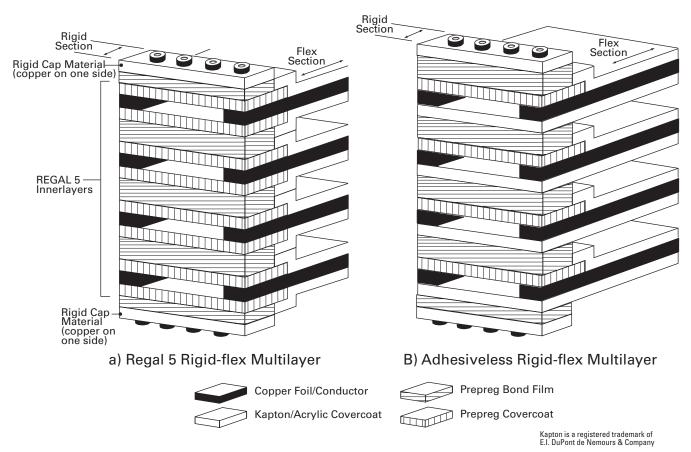

# **REGAL® Flex 5**

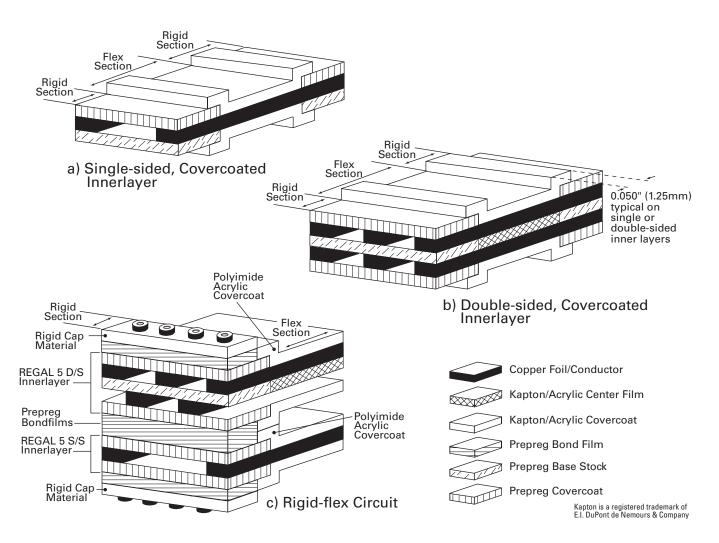

When flexibility requirements of the application require a bend radius equal to or greater than industry standards (refer to the *Mechanical Design* Section) for higher layer count rigid flex applications, REGAL<sup>®</sup> 5 processed laminates are recognized industry-wide as the ideal construction method. REGAL<sup>®</sup> 5 laminates pro-

Figure 2-15. REGAL<sup>®</sup> Flex 1 construction; a) single-sided covercoated innerlayer; b) double-sided covercoated innerlayer; c) multi-layer circuit.

vide a more homogeneous laminate in both the rigid and flexible areas. Teledyne accomplishes this be manufacturing dual core material innerlayers, which result in no polyimide or acrylic materials in the rigidized areas of the board, while assuring this material remains in the flexible areas to provide maximum flexibility. Refer to Figure 2-16.

These dual core material layers are selectively bonded together using the same manufacturing processes used to build the other rigid-flex constructions previously outlined. By utilizing this manufacturing technique, an ultra-high density, highly reliable, and thermally stable rigid-flex circuit can be designed and built in large quantities.

As with the REGAL<sup>®</sup> 1 construction technique, REGAL<sup>®</sup> 5 rigid-flex can be manufactured with singlesided or double-sided innerlayers. Single-sided innerlayers offer increased flexibility for certain applications, and the ability of having an odd number of flexible inner layers. REGAL<sup>®</sup> 5 double-sided innerlayers provide the option of having the increased flexibility of all thin-film flex materials in the flexible section, along with the option of two conductive layers bonded to a shared dielectric. This technique will enhance the performance of designs incorporating controlled impedance or other transmission line electrical properties that require multiple innerlayers with shielding.

There are some distinct advantages to the REGAL<sup>®</sup> Flex processing method when compared to other rigid-flex construction techniques:

• In particular the thermal stability of REGAL® Flex circuit boards; acrylic adhesives have a glass transition temperature (Tg) of 40°C and a CTE of 400-600 ppm/°C. The Z-axis expansion of a rigidflex using acrylic adhesive materials above Tg increases as the number of layers increases. The materials in a REGAL® Flex board have very specific thermal properties — the epoxy prepregs used have a Tg of 170°C and a coefficient of thermal expansion (CTE) of 70 ppm per degree C in the Z axis. The use of these materials yields a circuit board capable of passing a 290°C solder float for 10 seconds without exhibiting delamination or barrel cracks in the plated-through holes. This is due to the reduction in the Z-axis expansion rate of the laminated board. These advantages come at a

cost increase between REGAL® 1 and REGAL® 5 due to the increased processing complexity.

Conventional rigid-flex materials use a non-reinforced polyimide film as the base material. Since this material is dimensionally unstable during the manufacturing process, larger pad diameters on internal layers are required to compensate for the growth or shrinkage of the materials during processing. The increased pad diameters are needed so that after final lamination the manufacturer will have a greater chance of drilling down into the innerlayer pad at the drilling stage. It can be expected that a rigid-flex circuit incorporating an acrylic adhesive construction will exhibit high losses at the assembly stage due to delamination and barrel cracks. Because of the thermal stability of the REGAL<sup>®</sup> Flex materials, the board has the potential ability to withstand multiple wave solder operations without concern for creating failures.

REGAL<sup>®</sup> Flex innerlayers are constructed of a reinforced epoxy and fiberglass material that is woven to enhance X- and Y-axis stability. Because of the improved X- and Y-axis stability of the materials used when processing the innerlayers, multi-layer rigid-flex circuits designed for REGAL<sup>®</sup> Flex can achieve denser packaging. Smaller internal pads can be used along with tighter hole-to-hole spacing, which permits increased density and lower layer count.

Figure 2-16. REGAL<sup>®</sup> 5 construction; a) single-sided covercoated innerlayer; b) double-sided covercoated innerlayer; c) rigid-flex circuit.

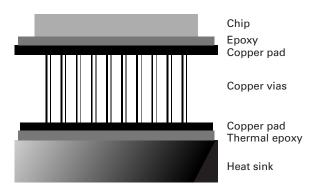

## Multi-Chip Modules (MCM)

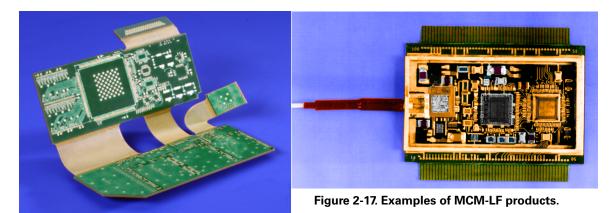

Multi-Chip Modules (MCMs) can be defined as structures consisting of two or more integrated circuit chips that are electrically connected to a common circuit base and interconnected by conductors within that base. There are three basic types of technologies that are used to manufacture MCM structures. The differences between the competing technologies are the dielectric materials and the processes used to manufacture the structures. The three types are as follows:

MCM-C – modules constructed on ceramic substrates using thick film (screen printing) technologies to form the conductor patterns.

MCM-D – modules whose interconnects are formed by thin film deposition of metals onto deposited dielectrics.

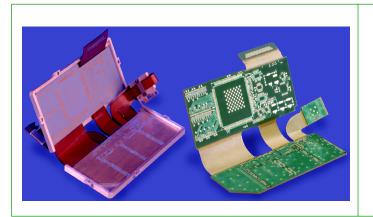

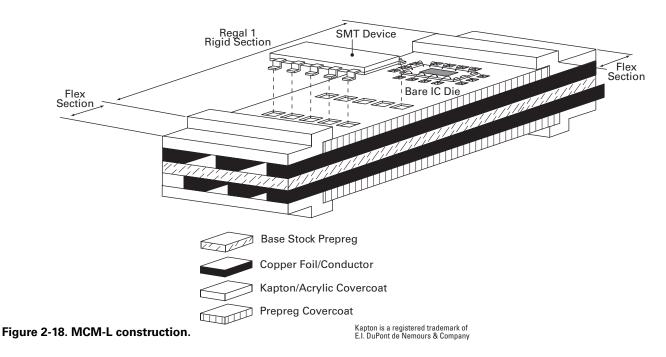

MCM-L – modules using advanced forms of printed wiring board technologies to form copper conductors on laminate based dielectrics. Refer to Figure 2-18.

The benefits of Multi-Chip Modules are:

- Increased system speed

- Reduced overall size

- Ability to handle chips with large numbers of I/O's

- Reduced number of external connections

Of the three types of MCM, laminate-based Multi-Chip Modules (MCM-L) offer the end-user the lowest cost, especially for higher volume applications. Lower costs are achievable because of lower raw material and processing costs, and through the use of large format array processing. Other benefits of MCM-L technology include two-sided assembly for both Chip-on-Board and surface mount components, large area substrates, and the reduction of connectors through the use of rigid flex substrates.

One shortcoming of MCM-L technology has been achieving high interconnect density using conventional manufacturing techniques. High density MCM-L's may

require additional design and engineering effort to obtain the interconnect density and performance required. To achieve the desired density, the design may incorporate smaller diameter drilled holes, blind and/or buried vias, and finer conductor widths and spacings. Many manufacturers are looking toward improved processing techniques and equipment to increase density. Processes such as micro-vias (vias less than 0.006" (150µm) in diameter) that are formed using advanced techniques such as laser drilling or plasma etching, and fine line imaging and etching will increase the circuit density without compromising yields. Another area of concern is the relatively larger coefficient of thermal expansion (CTE) of the substrates. The thermal mis-match between the substrate and the die limits the size of the die that can be reliably bonded directly to a laminate substrate. The mis-match can be somewhat mitigated by the use of epoxy underfill beneath the die, or by using thermally matched substrates. Performance enhancements may also come from the use of thinner dielectric materials, low loss dielectrics and better thermal management techniques.

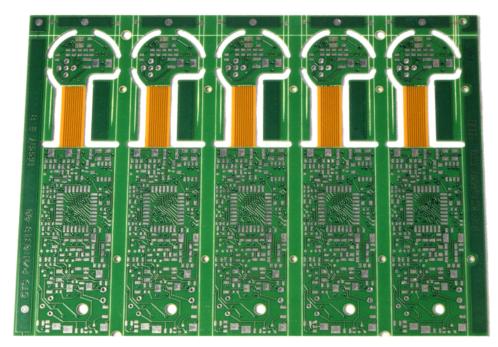

**Product Example**

# **Materials**

# **Chapter Terms**

Adhesiveless Laminates: A copper-clad laminate composite of polyimide film bonded to copper foil.

**Basestock or Base Material:** The insulating material upon which a conductive pattern may be formed. The basestock may be rigid or flexible, or both. It may be a dielectric or insulated metal sheet.

**Covercoat, Cover Lay or Cover Layer:** The layer of insulating material that is applied over a conductive pattern on the outer surface of a printed circuit. Used for electrical insulation and environmental sealing.

**Electro-deposited (Copper):** The deposition of a conductive material (copper) from a plating solution by the application of electrical current.

**Flexible Soldermask:** A soldermask that when cured over flexile circuits will not separate, fracture, or delaminate from that surface of the base material, conductors, and lands of the coated flexible wiring. IPC-TM-650,

TM 2.4.29 specifies a minimum number of 25 cycles using a 0.125"(3.175mm) diameter mandrel.

LPISM: Liquid photo-imageable soldermask.

**Reinforced Adhesive:** An adhesive material whose mechanical strength is improved by the addition of glass fibers.

**Soldermask:** A resist that provides protection from the action of solder.

**Tenting:** The covering of holes in a printed board and the surrounding conductive pattern with a resist that is usually a dry film.

**Thermoset Adhesive:** An adhesive material that undergoes a chemical reaction when exposed to elevated temperatures that leads to it having a relatively infusable or crosslinked state that cannot be softened or reshaped by subsequent heating.

## **Materials**

# **Conductive Materials**

Thin copper foil is the most readily available and economical conductive material for flexible circuitry. Copper foil is available in two types, each with different properties.

The first type of copper foil is electro-deposited foil, which can be laminated to a dielectric to form basestock. Some of the advantages of this type of copper foil are:

- economical

- rougher base bonding surface which enhances bonding

- vertical grain structure, which enhances fine line etching

The second type is rolled copper foil, normally available fully annealed, but also supplied as low temperature annealed. Rolled annealed copper foil is the type commonly used by flexible circuit manufacturers because of its flexing characteristics. Some of the advantages of this foil are:

- horizontal grain structure better suited for flexing applications

- can be supplied with a bond enhancer to aid in adhesion

- can be supplied with bond enhancer on both sides of the foil to reduce processing steps and handling

- can be double treated, which adds oxide treatment to the surface of the copper to greatly increase bond strength

Both foil types are readily available in various weights/ thicknesses. Table 3-1 shows the more common thickness and their equivalent weights for a one square foot of copper foil of a given thickness. These foils are the easiest to handle and the most economical to process. They are readily available as straight foil, or can be prelaminated to a base dielectric material.

## COPPER FOIL THICKNESS AND WEIGHT COMPARISON

| Weight               | Thickness |       |  |

|----------------------|-----------|-------|--|

| <sup>1/2</sup> ounce | 0.0007"   | 17µm  |  |

| 1 ounce              | 0.0014"   | 35µm  |  |

| 2 ounce              | 0.0028"   | 70µm  |  |

| 3 ounce              | 0.0042"   | 105µm |  |

|                      |           |       |  |

Table 3-1.

# **Surface Treatments**

The surfaces of both copper types are normally treated by chemical oxidation to increase adhesion, to reduce resist undercutting by etchants, and to reduce bond degradation by plating chemicals. Electro-deposited copper is more easily treated and less expensive to treat than rolled copper. A thin layer of zinc applied to the copper foil's surface will increase bond strength and reduce corrosion. Other proprietary, stain-proofing treatments are also used.

# **Foil Grades**

Copper foils come in a variety of quality and property grades. To avoid excessive foil defects, only the highest printed circuit quality electro-deposited copper should be used for flexible circuits. Both annealed and nonannealed electro-deposited copper foil are available. A special high ductility grade of electro-deposited copper called high tensile elongation (HTE) is available which possesses the physical property of increased elongation. Rolled copper is available in a special low temperature annealed (LTA) grade which is easier to handle and harder than ordinary soft rolled copper. LTA foil is annealed during lamination to a dielectric substrate.

The properties of electro-deposited and rolled, annealed copper are compared in Table 3-2.

## **PROPERTIES OF COPPER FOILS (1 OZ.)**

| PROPERTY                          | ELECTRO-<br>DEPOSITED<br>(High ductility) | ROLLED,<br>ANNEALED             |

|-----------------------------------|-------------------------------------------|---------------------------------|

| Purity                            | 99.8%                                     | 99.9%                           |

| Resistivity<br>(at 20° C)         | $16\Omega \text{ g/cm}^2$                 | 15.2 $\Omega$ g/cm <sup>2</sup> |

| Tensile<br>strength @<br>23°C     | 40kpsi                                    | 20kpsi                          |

| Tensile<br>strength<br>@180°C     | 20kpsi                                    | 14kpsi                          |

| Ductility elongation <sup>2</sup> | 3%                                        | 10%                             |

| Standard<br>weights               | <sup>1</sup> /8 - <b>20 oz.</b>           | <sup>1</sup> /2 - 6 oz.         |

| Table 2.2                         |                                           |                                 |

Table 3-2.

# **Other Metals Used in Printed Wiring Boards**

Aluminum is used for electrical shielding or to replace copper in low cost circuits. It cannot be soldered or welded with conventional equipment.

Nickel, because of its hardness and ease of welding, is used to join components to substrates which cannot withstand ordinary solder temperatures. Both electroplated and rolled nickel are available.

Gold provides excellent corrosion resistance. Since it is extremely soft and very expensive, it is used sparingly, often as a plating.

Silver, with the highest conductivity of all metals, is frequently used as a contact material.

**Copper Alloys:** Phosphor bronze and beryllium copper foil provide circuitry with integral leaf springs and corrosion resistant contacts where precious metal plating is not required.

**Ferrous Alloys:** Soft ferromagnetic foils are used for magnetic shielding. Stainless steel foil is used for resistance heaters and circuits requiring high strength and corrosion resistance.

Nickel Alloys: Copper-nickel alloys, such as Monel<sup>®</sup>, are used for corrosion resistance. Nickel-chromium

alloys, such as Inconel<sup>®</sup>, provide high electrical resistance for flexible heating elements.

# **Flexible Dielectric Materials**

The design and use of flexible circuitry has been made possible by the availability of numerous flexible thin film dielectric materials. Each of these materials has properties which dictate where they are best used. When choosing a dielectric insulating film, there are many factors that should be considered, including operating environment, mechanical constraints of the material, electrical characteristics, and cost.

Some materials have qualities which make them well suited for the operating conditions of the final assembly, but they may not have the necessary chemical, mechanical or thermal properties necessary to withstand a manufacturing environment. To ensure that the correct material can be used for a particular application, overall environmental and manufacturing conditions to which the assembly will be subjected must be carefully analyzed.

Tables 3-4 and 3-5 list the characteristics of some high temperature thin film dielectrics. These films tolerate high

| FOIL     | ELECTRICAL RESISTANCE<br>at 20° C |                              | DENSITY                  | THERMAL<br>CONDUCTIVITY    | THERMAL<br>EXPANSION<br>COEFFICIENT | MATERIAL<br>RESISTIVITY<br>COMPARED<br>TO COPPER* |

|----------|-----------------------------------|------------------------------|--------------------------|----------------------------|-------------------------------------|---------------------------------------------------|

|          | Ohms mil<br>per ft.               | micro<br>ohms – sq.<br>cm/cm | lb. per<br>cubic<br>inch | btu/hour/sq.<br>ft./°F/ft. | ppm/ °F                             |                                                   |

| Aluminum | 17                                | 2.8                          | .097                     | 118                        | 13.0                                | 1.635                                             |

| Copper   | 10.4                              | 1.7                          | .324                     | 223                        | 9.0                                 | 1.000                                             |

| Gold     | 14.7                              | 2.4                          | .698                     | 170                        | 7.8                                 | 1.41                                              |

| Iron     | 60                                | 10.1                         | .284                     | 35                         | 6.5                                 | 5.68                                              |

| Lead     | 132                               | 22.0                         | .410                     | 20                         | 16.3                                | 12.69                                             |

| Nickel   | 51                                | 8.5                          | .322                     | 35                         | 7.0                                 | 5.77                                              |

| Silver   | 9.8                               | 1.6                          | .379                     | 240                        | 10.2                                | 0.942                                             |

| Tin      | 70                                | 11.6                         | .264                     | 35                         | 14.9                                | 6.73                                              |

**PROPERTIES OF VARIOUS CONDUCTIVE METALS**

\*To compare resistance of material to that of copper of equal size.

Table 3-3.

## **Materials**

| CHARACTERISTIC           | UNIT OF<br>MEASURE | POLYIMIDE<br>FILM | <b>FEP</b><br>FILM | POLYESTER<br>FILM |  |

|--------------------------|--------------------|-------------------|--------------------|-------------------|--|

| Dielectric Strength      | V/Mil-1 Mil        | 4500              | 5000               | 7000              |  |

| Dielectric Constant      | 1 kHz              | 3.4               | 2.1                | 3.1               |  |

| Dissipation Factor       | 1 kHz              | .0016             | .0003              | .005              |  |

| Tensile Strength         | PSI                | 20000             | 4000               | 25000             |  |

| Elongation               | %                  | 70                | 300                | 100               |  |

| Water Absorption         | % By Weight        | 3                 | < .01              | .8                |  |

| Operating Temperature    | °C                 | 150               | 204                | 149               |  |

| Absolute Max Temperature | °C                 | 300               | 274                | 149               |  |

| LowTemp. Embrittlement   | °C                 | -55               | -85                | -50               |  |

| Melt Point               | °C                 | 816               | 280                | 248               |  |

| Weather Resistance       | MIL-STD-2026       | Excellent         | Excellent          | Fair              |  |

| Fungus Resistance        | MIL-E-5272         | Non-Nutrient      | Non-Nutrient       | Non-Nutrient      |  |

| Chemical Resistance      | N/A                | Excellent         | Excellent          | Excellent         |  |

# **CHARACTERISTICS OF THIN FILM DIELECTRICS**

### Table 3-4.

volume assembly techniques, such as wave soldering, and multiple soldering operations without degradation.

# **Uses of Dielectric Films**

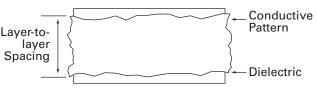

When used on a flexible circuit, insulating dielectric films can function as a base film or a covercoat film.

The base dielectric film is used to support and protect the copper foil during the manufacturing process. It can also provide electrical protection (insulation) and environmental protection to the circuit. Different thicknesses of dielectric films may also be used to control impedance. The copper foil is bonded to the base dielectric prior to the imaging operation. The dielectric film therefore acts as an etch resist on the backside of the sheet on single layer flexible circuits. On double-layer applications, the base dielectric is sandwiched between two copper foils. This provides support and prevents etching on the backside of the copper foils.

The covercoat dielectric is thermally bonded to the base dielectric after the conductive pattern has been etched. The covercoat serves to protect the copper conductors from moisture, contamination and damage.

# **Adhesives**

There are several types of adhesives from which to select, each with its own unique properties. The two main categories are thermoset flexible and reinforced adhesives. Within these categories are several choices. The selection of the proper adhesive and thickness to bond the conductive copper and dielectric is considered to be one of the most critical choices in flexible and rigid-flex circuitry design.

# **Thermoset Flexible Adhesives**

Thermoset adhesives are used to bond flexible dielectric film to copper foil and to bond multiple layers together to form multi-layer flexible circuits. Two types of flexible thermoset adhesives — modified acrylic and epoxy — are available for processing flexible circuitry. They have different characteristics and are chosen for the specific application requirements.

# **Modified Acrylic Adhesive**

Acrylic adhesives have been available for use in flexible circuitry manufacturing since the early 1970's. They

offer excellent adhesion to both the polyimide films and copper.

Typical bond strengths to treated rolled annealed copper are:

- 8-15 lbs./inch at room temperature

- 8-15 lbs./inch after solder float

- 7-14 lbs./inch after solder immersion

Other characteristics of acrylic adhesives are:

- thermal stability to resist multiple exposure to molten solder and hot oil reflow

- will pass UL tests for flammability at VO rating

- chemical resistance to withstand exposure to a wide variety of chemicals and solvents used in processing

- controlled flow of cover sheets and bond films

- easy processing

- batch-to-batch consistency

- excellent thermal resistance in heated environments

- repairability in the most demanding of environments

Modified acrylic adhesives do have some properties that adversely affect multi-layer circuit processing. First, their moisture absorption rate is approximately 4% by weight. Moisture can be successfully removed by baking prior to soldering. In multi-layer processing, however, adhesives are buried beneath several layers of other materials, requiring longer baking cycles to remove all the moisture.

Second, acrylic adhesives have a relatively low glass transition temperature (Tg), 40°C, and a coefficient of thermal expansion (CTE) of 400-600 ppm, higher than other bonding materials. When several layers of acrylic adhesive are used in a circuit board, such as in multi-layer flex and rigid-flex, these characteristics lead to defects. Z-axis movement of these materials can cause delamination and barrel cracks in plated-through holes.

Please refer to the *REGAL® Flex* discussion in Chapter 2 of this Design Guide to see how Teledyne has addressed these shortcomings.

# **Epoxy Adhesives**

Prior to discovery of the superior flow characteristics, bond strength and temperature resistance of acrylic adhesives, modified epoxy materials were the material of choice for single-sided and double-sided flexible circuits. In multi-layer and rigid-flex circuits, however, epoxies are increasingly used because of their superior Z-axis expansion characteristics and lower moisture

| Property                       | Polyimide (Kapton)          | FEP                                                                                 | Polyester         |  |

|--------------------------------|-----------------------------|-------------------------------------------------------------------------------------|-------------------|--|

| Tensile Strength               | Very high                   | Low                                                                                 | Extremely high    |  |

| Manufacturing Limita-<br>tions | Few to none                 | Few to noneAdhesionSensitive toproblems, lowing chemicaltensile strengthdering temp |                   |  |

| Flammability                   | Non-flammable               | Melts                                                                               | High              |  |

| Moisture Absorption            | Highest                     | Lower                                                                               | Lowest            |  |

| Dimensional Stability          | Unstable                    | Unstable                                                                            | Stable            |  |

| Flexible                       | Yes                         | Poorly                                                                              | Yes               |  |

| Bondable                       | Yes                         | Yes                                                                                 | Yes               |  |

| Relative Cost                  | Moderate                    | Expensive                                                                           | Inexpensive       |  |

| Typical Use                    | Most widely used insulation | Excellent dielec-<br>tric                                                           | Consumer-oriented |  |

FEATURE COMPARISON OF COMMON FILM MATERIALS

Kapton is a registered trademark of E.I. DuPont de Nemours & Company **Table 3-5.**

## **Materials**

absorption rate. Some of these epoxies also offer improved flexibility compared to acrylic based systems.

Bond strengths to treated rolled annealed copper are:

- 10-15 lbs./inch at room temperature

- 8-12 lbs./inch after solder float

- 8-12 lbs./inch after temperature cycling

Other characteristics of epoxy based adhesives are:

- thermal stability to resist multiple soldering operations

- chemical resistance to withstand multiple exposures to processing chemicals and cleaning solvents

- controlled flow

- batch-to-batch processing

- will pass UL tests for flammability at V1 or V0 rating

- moisture absorption rate as low as 1.5% by weight

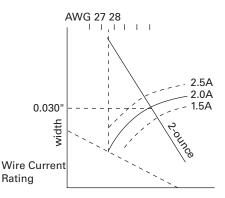

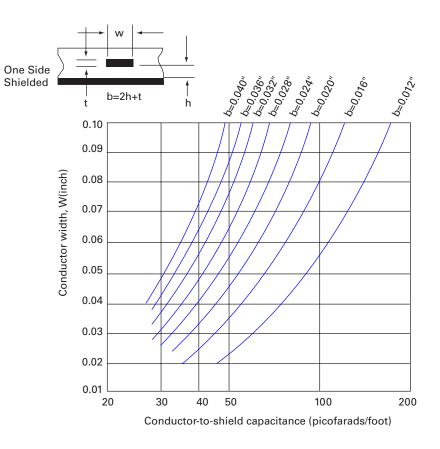

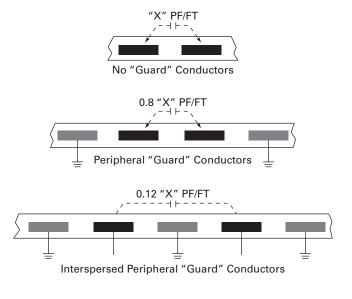

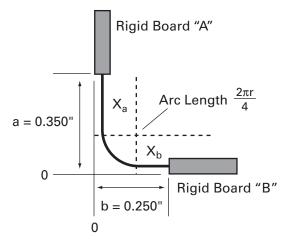

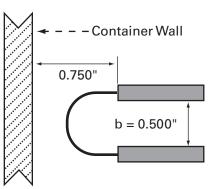

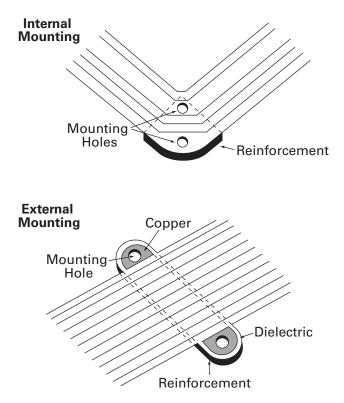

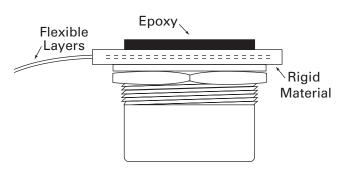

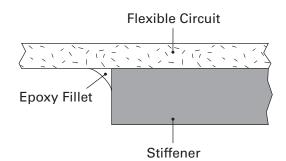

## **Reinforced Adhesive Materials**